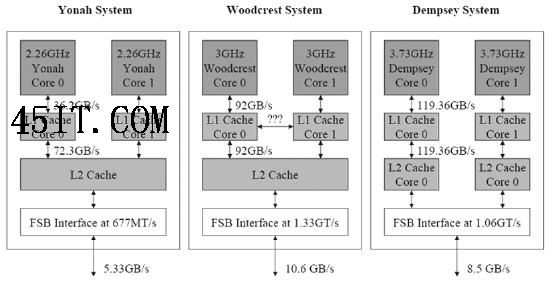

Yonah、Woodcrest(Core)與Dempsey處理器的結(jié)構(gòu)對(duì)比。Core繼承了Yonah的雙核心設(shè)計(jì)方式―共享L2緩存和系統(tǒng)總線接口,同時(shí)增加了L1緩存之間的通訊;不過Core的內(nèi)部帶寬更接近Dempsey,片上緩存的帶寬遠(yuǎn)遠(yuǎn)超過Yonah,同時(shí)系統(tǒng)總線的帶寬也有大幅提升 Core架構(gòu)延續(xù)了Yonah的這一特性,因此服務(wù)器版本(Woodcrest)將比前代產(chǎn)品(Dempsey)提供更好的性能。此外,英特爾方面多次提到Core架構(gòu)還可能實(shí)現(xiàn)在L1緩存之間直接傳輸數(shù)據(jù),不過到目前為止英特爾對(duì)此并沒有透露更多的細(xì)節(jié),但我們可以相信如果這是真的話,Core的性能無(wú)疑會(huì)再提升一個(gè)檔次。

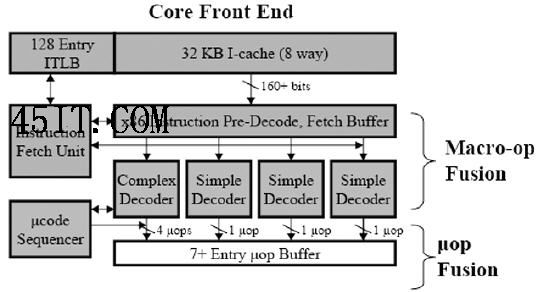

三、指令融合和分支預(yù)測(cè)體系 此次英特爾從NetBurst架構(gòu)到Core架構(gòu)的轉(zhuǎn)型,還有一項(xiàng)非常明顯的改進(jìn)。那就是x86指令的融合,它可以說(shuō)是Core架構(gòu)獨(dú)有的特性之一(圖3)。

在處理器內(nèi)部,x86指令被稱為Macro-ops,而內(nèi)部指令被稱為uops,而Macro-ops融合可以將兩個(gè)Macro-ops融合成一個(gè)uops。舉個(gè)例子來(lái)說(shuō),我們可以把x86 Compare(比較)指令與x86 Jump(跳轉(zhuǎn))指令融合在一起,生成一條單獨(dú)的uops(比較并跳轉(zhuǎn)指令)。在Core中每個(gè)解碼器都可以完成這樣的優(yōu)化工作,但是每周期內(nèi)最多只能有一個(gè)解碼器完成這樣的融合,所以最大指令解碼帶寬是每周期4 1個(gè)x86指令。

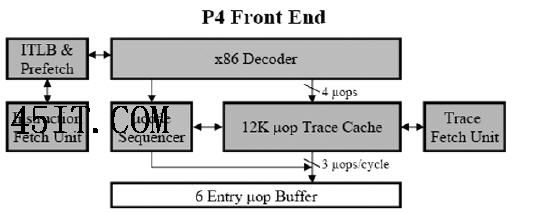

對(duì)比英特爾不同架構(gòu)中的提取指令/譯碼單元,可以看到Core要比Yonah和Pentium 4更加復(fù)雜 這種融合的好處是顯而易見的:首先,融合之后需要執(zhí)行的指令變少了,這等于直接提高了處理器的執(zhí)行性能;其次,亂序執(zhí)行可以因此變得更有效率,因?yàn)槿诤系倪^程實(shí)際上就是讓指令窗口檢查更多的程序代碼,更大限度地發(fā)現(xiàn)指令之間的并行性,從而提高處理器的執(zhí)行效率。不過頗具諷刺意味的是,從某種程度上來(lái)看這種x86指令的融合機(jī)制使得x86處理器更加RISC(簡(jiǎn)單指令集)化而不是CISC(復(fù)雜指令集)化。

為了降低長(zhǎng)流水線帶來(lái)的負(fù)面影響,英特爾曾經(jīng)在NetBurst架構(gòu)的分支預(yù)測(cè)上花費(fèi)了相當(dāng)大的精力,其分支預(yù)測(cè)的錯(cuò)誤率號(hào)稱比上一代架構(gòu)下降了33%以上,而Core架構(gòu)的分支預(yù)測(cè)能力在NetBurst的基礎(chǔ)上又有進(jìn)步。

在新架構(gòu)中,英特爾不僅保留了上一代架構(gòu)的跳轉(zhuǎn)目標(biāo)緩沖區(qū)、跳轉(zhuǎn)地址計(jì)算器以及返回地址堆棧,而且還采用兩種新的預(yù)測(cè)算法―“循環(huán)探測(cè)”能夠正確探測(cè)(程序的)循環(huán)退出,而“間接分支預(yù)測(cè)”可以基于全局的歷史信息獲取(預(yù)測(cè))正確的目標(biāo)地址。除此之外,Core架構(gòu)還引入了其它的一些新特性,例如在原先的架構(gòu)中,跳轉(zhuǎn)命令總會(huì)引入一個(gè)周期的流水線空置,但是在Core架構(gòu)中引入了一個(gè)用于存儲(chǔ)跳轉(zhuǎn)發(fā)生位置的隊(duì)列,大部分的流水線空置都將被消除。諸多新特性的引入,使得Core的分支預(yù)測(cè)能力空前強(qiáng)大,從性能上來(lái)說(shuō)無(wú)異于如虎添翼。

|

新聞熱點(diǎn)

疑難解答

圖片精選